CSE

# CSE4210 Architecture and Hardware for DSP Lecture 2 Fast Addition

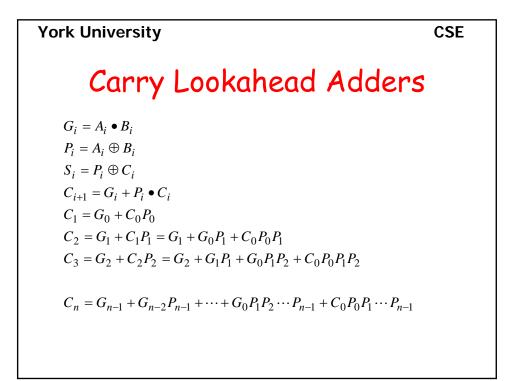

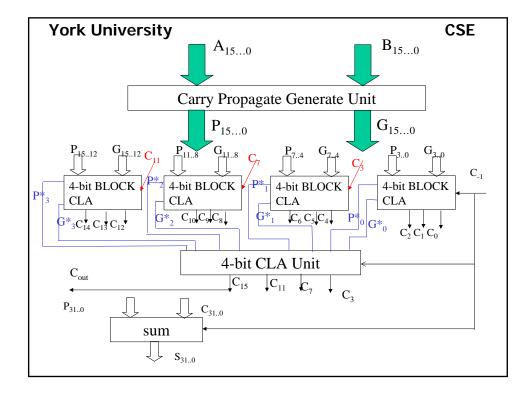

#### Carry Lookahead Adders

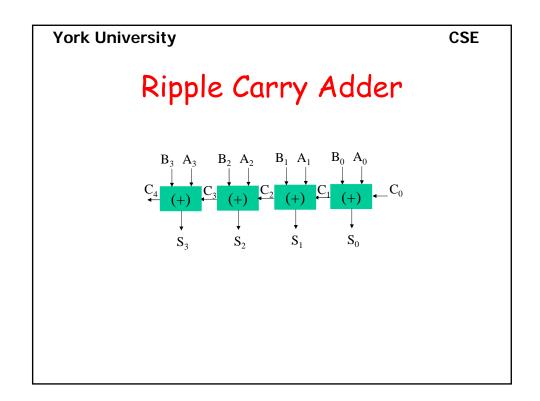

- Time = Carry generate/propagate + carry lookahead (to generate C's)+ sum (EXOR) = 3+2+2=7 gate delays.

- The problem is we need n-input AND, for 32 or 64-bit numbers that is not practical.

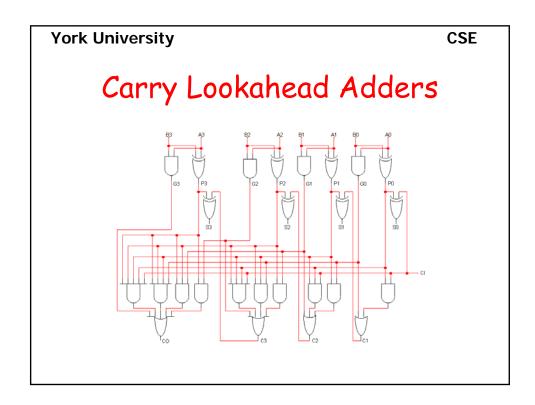

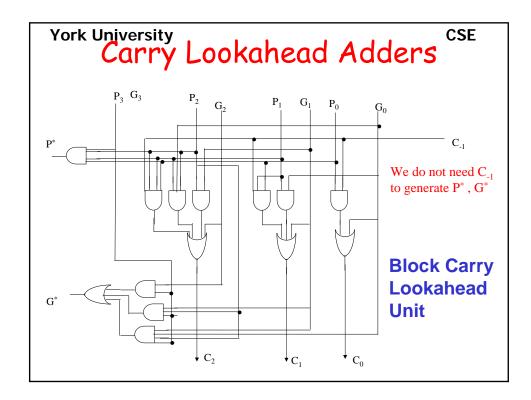

#### Carry Lookahead Adders

- In order to limit the fan-in in the carry generation circuitry, we use block carry lookahead adders.

- Consider for examples the number is divided into blocks each of 4 bits.

- That means the fan-in will be limited to 4 (not 5)

- Each block has a block carry generate G\* and block carry propagate P\*

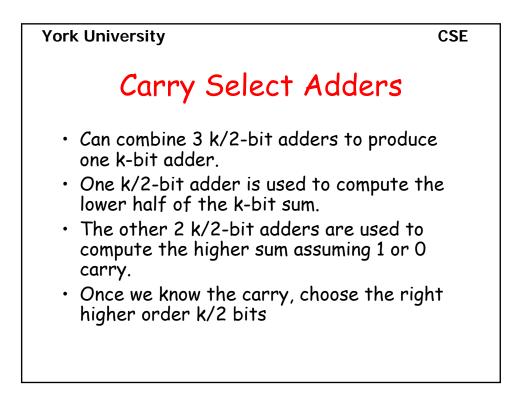

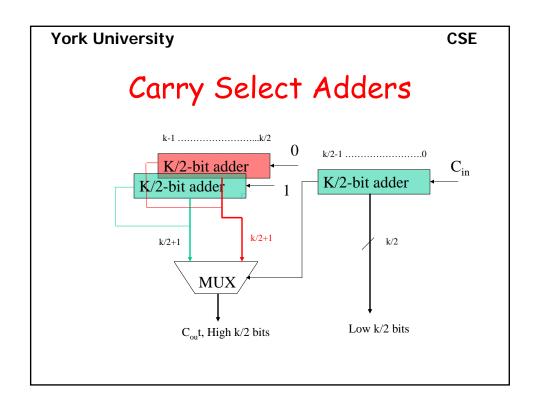

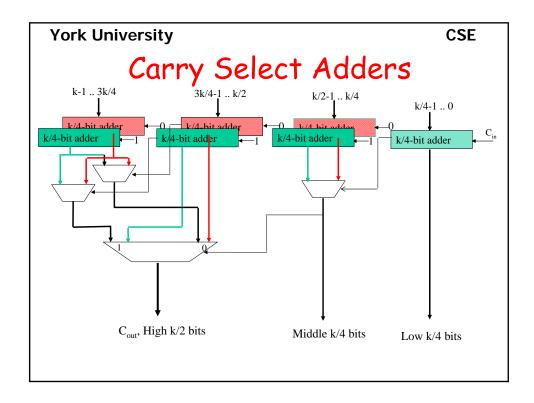

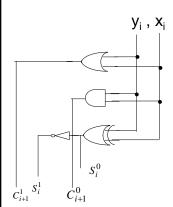

## Carry Select Adders

- The idea is instead of waiting for the carry from the right, we compute two sums.

- One assuming the carry is 0

- The other assuming the carry is 1

- Once we know the carry, then we can select the right sum using a mux

# Carry Select Adders

CSE

• What is the time and cost of CSA?

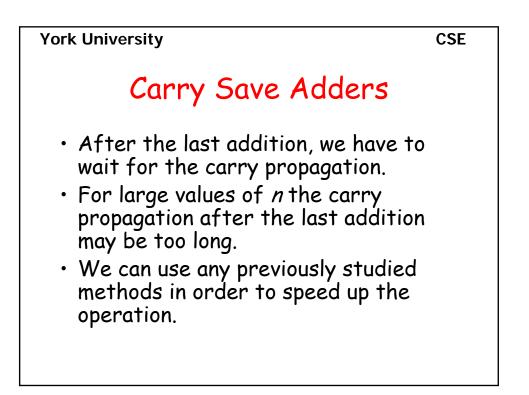

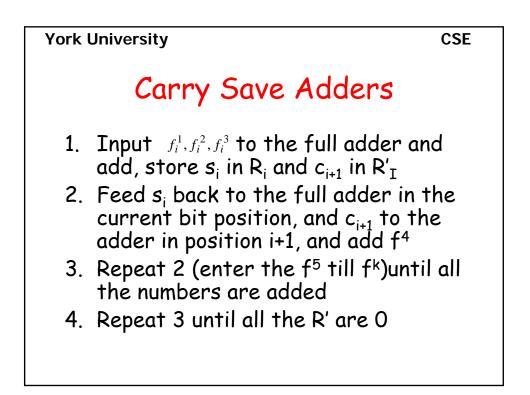

## Carry Save Adders

- So far, we mentioned adders that add 2 numbers.

- In multiplication (and accumulation) we may want to add more than 2 numbers.

- Instead of waiting for the carry propagation of the first addition, to be completed, before starting the second addition, we overlap the carry of the first addition with the computation of the second addition. ....

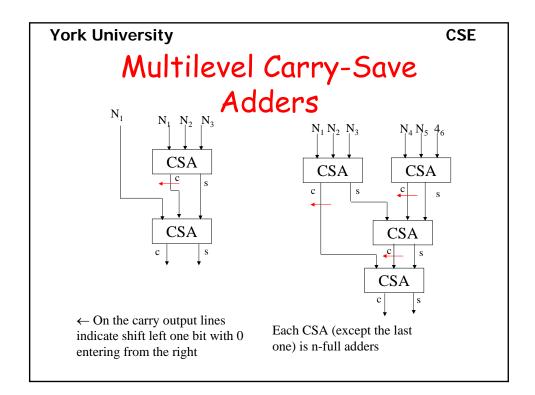

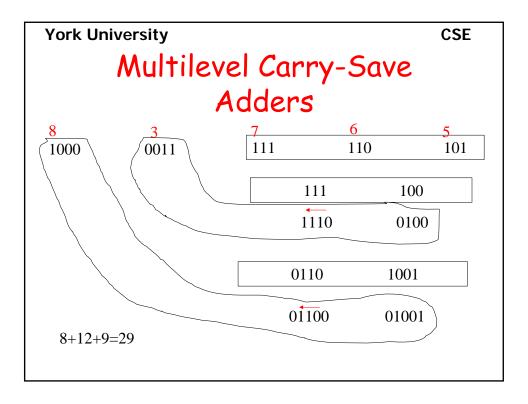

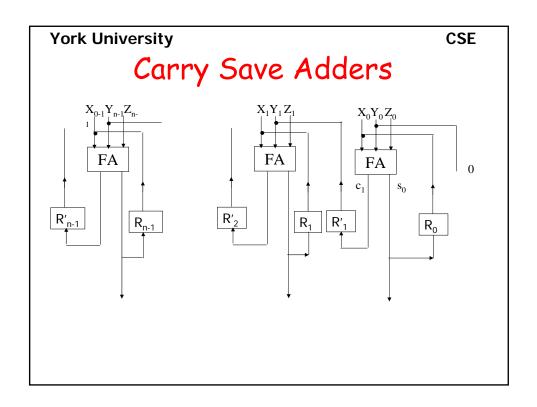

### Multilevel Carry-Save Adders

- The previous design still inputs one additional number per cycle.

- CSA tree can be sued to add k numbers simultaneously.

- Two feedback inputs in each case are needed to accumulate the partial sum and the one-bit left-shifted partial carry